University of Thi -Qar Journal for Engineering Sciences http://www.doi.org/10.31663/tqujes.12.2.451(2022) Vol 12.2( December 2022) ISSN :2664- 5572 ( online) ISSN:2664-5564 (print) Available at <u>http://jeng.utq.edu.iq</u> utjeng@ utq.edu.iq

## Seven-Level Inverter Topology with Fewer Switching Components

Hussein S. Abdulazeez<sup>†</sup>, Rabee' H. Thejel<sup>‡,</sup> and Diyah K. Shary<sup>†</sup>

<sup>†</sup>Basrah Engineering Technical College, Southern Technical University, Iraq, h.s.abdulazziz@stu.edu.iq <sup>‡</sup>Basrah Engineering Technical College, Southern Technical University, Iraq, rabee\_alabbasi@stu.edu.iq

<sup>†</sup> Basrah Engineering Technical College, Southern Technical University, Iraq, diyahpower@stu.edu.iq

#### Abstract

This work proposed a 7-level Inverter structure with minimum power components and controlling with pulse width modulation (PWM) techniques. This topology has three times the greater capacity for voltage boosting. The aim of this study is achieved using a single voltage source, eight switches, two diodes, and two capacitors. Three times voltage boosting, a small number of switches, reduced voltage stress, and a self-balanced capacitor is the main characteristics of this topology. The selective harmonic elimination pulse width modulation SHE-PWM technique, which is based on genetic algorithm optimization, is also used to isolate or eliminate undesirable low-order harmonics of the output voltage. To demonstrate the aforementioned benefits, a simulation was performed using MATLAB SIMULINK, and the corresponding THD results were compared with various modulation indices.

Keywords: - Multilevel inverter, switched capacitors, PWM technique, Voltage boosting ability.

#### 1. Introduction

In recent years, multilevel inverters (**MLIs**) as a feasible solution for high-efficiency electric powerelectronic conversion systems.

The primary reasons for using MLIs in a wide range of applications, including motor drives and the use of Solar and wind energy sources, to name a few, are their intrinsic characteristics, such as reduced voltage stress on power electronic semiconductor switches, for switching in low frequency, the efficient output waveform, minimum filter requirement, etc.[1]. The basic multilevel inverters MLIs are listed as 1-Diode-Clamped (DC-MLI) 2-Flyingcapacitors (FC-MLI) 3-Cascaded H-bridge(CHB-MLI)[2] Additionally, CHB-MLI needs many isolated dc sources, whereas NPC-MLI and FLC-MLI still struggle with the balance of capacitor voltages. Although there are numerous variations of these fundamental MLIs, such as symmetric cascade H-bridge (S-CHB), asymmetric Cascade H-Bridge (A-CHB), hybrid Neutral point clamped(NPC) with Cascade H-bridge CHB, etc., The overall structure increases the complexity of control by involving a large number of components [3]. The electrical energy produced by renewable energy sources, such as photovoltaic (PV) arrays and fuel cells, is mostly low dc voltage and must be converted to higher ac voltage. One of the common approaches is to pair a front-end conventional MLI with a back-end dc-dc boost converter [4]. As an alternative, switched-capacitor multilevel inverters (SC-MLIs) have been thoroughly researched as a new approach strategy to dealing with the issues listed above. Here, a switched-capacitor-based multilevel boost inverter was introduced in [5] while having no inductive-load ability, it helps to build seven levels with fewer components than standard topologies. Although the main aim of SC-MLIs is buck-type devices, some systems that use solar photovoltaics, fuel cells, or electric car batteries need

additional boosting circuits **[6].** Furthermore, by eliminating the requirement for an additional boosting circuit, The circuit is simpler as a result of the fundamental idea of connecting SCs in parallel or series with the input voltage source **[7]-[8].**

To construct a structure with as few components as possible, a variety of MLIs for more voltage levels have been described in the literature due to the advantages of the SC technique. Ten switches and four dc sources are used in a thirteen-level (13-L) inverter [9]. It is created in ML's kite structure in [10]. . another kite-type with switched capacitance-voltage (K-Type SC-MLIs) which needed fourteen semiconductor switches, four capacitors, and a single dc source is presented in [11 According to the literature review, it is evident that attempting to increase the output level causes the circuit to become more complex. Implementation is more expensive. Consequently, numerous investigations were conducted in the literature that has a big impact on reducing the consumption of various elements including voltage sources, power semiconductors, and switched capacitors. This study described a seven-level SC-based inverter with a three-voltage boosting gain. The following are a few of this topology's advantages:

To produce seven levels of synthesized output voltage, only eight power switches and two diodes are needed (Vo).

It only needs two balanced switched capacitors, and no additional circuits, sensors, or complicated control techniques.

3. inherent ability to change the polarity.

4. In the proposed technology, there are eight switches in total, but only four of them are active at any given voltage level, which significantly lowers power switching losses.

Section 2 provides a detailed description of the circuit, operating modes for the proposed seven-level inverter, and

the developed pulse width modulation (PWM) scheme. In section 3, it was discussed how to optimize SHE-PWM using a genetic algorithm to implement it in the suggested topology. A thorough comparison with the current topology is presented in section 4 using various metrics. The findings are discussed in section 5. The conclusion is included in section 6.

#### 2- Proposed 7-level inverter

#### **2.1 Circuit Description:**

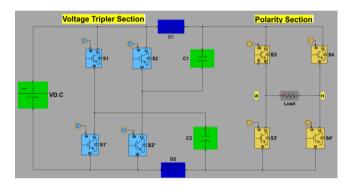

The seven-level multilevel structure with a switched capacitor is shown in Fig. 1. It includes a single DC source, eight switches, two diodes  $(D_1, D_2)$ , and two capacitors  $(C_1, C_2)$ . There are four complementary switches  $(S_1, S_2, S_3, \text{ and } S_4)$ . Van represents the inverter's output as determined by the source voltage (Vdc).

Fig.1 Proposed 7- level MLI structure

The topology here comprises two parts, The first part is a and source voltage Vdc) of and is responsible for boosting the voltage to three times the input voltage, as shown on the left of Fig.1. The second is a polarity part is working together with the first part and contains four switches (S<sub>3</sub>, S<sub>3</sub>', S<sub>4</sub>, and S'<sub>4</sub>, and load) to reverse the polarity of the part (H-bridge).as shown on the right of Fig.1. If  $C_1$  and  $C_2$  are large enough just to keep a constant dc voltage without considering the forward voltage drop and on-state resistance of the switching devices and without the need for any closed-loop control, three different dc-bus voltages (Vdc-bus) can be produced. In other words, the series/parallel connection technique ensures the self-voltage balancing of SCs. Each component has experienced low voltage stress (Vdc). The proposed inverter is less complicated and more affordable because of this feature.

# 2.2 The Principle of Operation and SC Voltage Balancing:

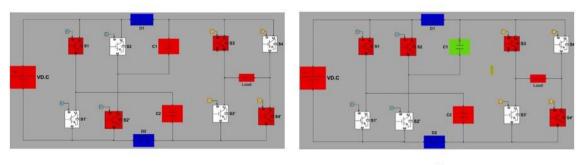

The current flow path for a resistive load is shown in Fig. 2 following the switching states in Table I. The nine operating states in the suggested topology have been completed by

each cycle of operations. The switching table indicates the entry "1" for the ON state and "0" for the OFF state. to

fully charge each capacitor ( $C_1$  and  $C_2$ ) to its maximum source voltage(Vdc) rating. the capacitors C1 and C2 are parallel connected to the source voltage in the voltage tripler section to  $C_1$  and  $C_2$  in charging operation. while capacitors discharged by connecting in series with the source Vdc, These two capacitors simultaneously discharged to the source and the load. in three voltage levels, self-voltage balancing of capacitors is ensured by connecting them in parallel for charging and in series to discharge. Capacitors  $C_1$  and  $C_2$  are connected in parallel with the Vdc during the voltage levels  $\pm 1$ Vdc, therefore, as a result, charged at level ±1Vdc. Depending on the selected switch state, either  $C_1$  or  $C_2$  discharges at voltage levels below  $\pm 2Vdc$  while the other charges are, two capacitors in series with input source discharges, The operating modes are:

**1-Vab=0V**: During this state as shown in Fig 2 d, through the power semiconductor devices  $(S_1', S_2 \text{ and } S_3', S_4')$  in the ON state position. the capacitors are not charged (idle), the canceling voltage across the load by  $(S_3', S_4')$ . As a result, the load receives zero voltage.

**2-Vab=Vdc**: The state explains the capacitors  $C_1$  and  $C_2$  are simultaneously charged by the source voltage to produce load voltage(**Vdc**), with the power switches devices (**S1**, **S2'**, **S3**, **and S4'**) in the ON state. In a similar manner, switches (**S1**, **S2'**, **S3'**, **and S4**) are activated in a negative operation mode. The useful mode of operation is proved in Fig .2 a.

**3-Vab=2Vdc**: During this state, the load voltage **2Vdc** is obtained by switching ON the switches under Table I in states 2 and 3.

**4-Vab=3Vdc**: During this state 4, the input voltage to supply is coupled in series with the voltage storing devices capacitors  $C_1$  and  $C_2$ , and the load voltage when  $(S_2, S_1', S_3, \text{ and } S_4')$  are ON so, the total gain of state 4 is **3Vdc** alternated.

Table 1

Switching states of a proposed 7-level inverter.

| Stat | Tripler |   | Polarity |   | Capacitors |           | Van   |

|------|---------|---|----------|---|------------|-----------|-------|

| es   | circuit |   | circuit  |   |            |           |       |

| 1    | 1       | 0 | 1        | 0 | charge     | Charge    | +Vdc  |

| 2    | 1       | 1 | 1        | 0 | Discharge  | charge    | +2Vdc |

| 3    | 0       | 0 | 1        | 0 | charge     | Discharge | +2Vdc |

| 4    | 0       | 1 | 1        | 0 | Discharge  | Discharge | +3Vdc |

| 5    | 0       | 1 | 0        | 0 | Idle       | Idle      | 0     |

| 6    | 1       | 0 | 0        | 1 | charge     | charge    | -Vdc  |

| 7    | 0       | 0 | 0        | 1 | Discharge  | charge    | -2Vdc |

| 8    | 1       | 1 | 0        | 1 | charge     | Discharge | -2Vdc |

| 9    | 0       | 1 | 0        | 1 | Discharge  | Discharge | -3Vdc |

Fig.2 Modes of operation for 7-level MLIs with positive half-cycle and zero states. (a) stage 1 +1 Vdc.(b)Stage 2 = +2Vdc.(c)Stage=+3Vdc.(d) Stage 4 = 0 V

### 2.3 PWM Strategy

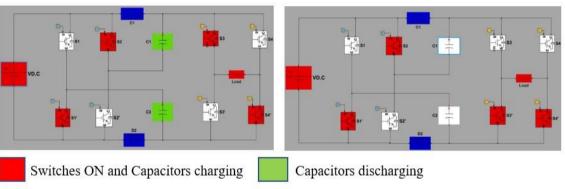

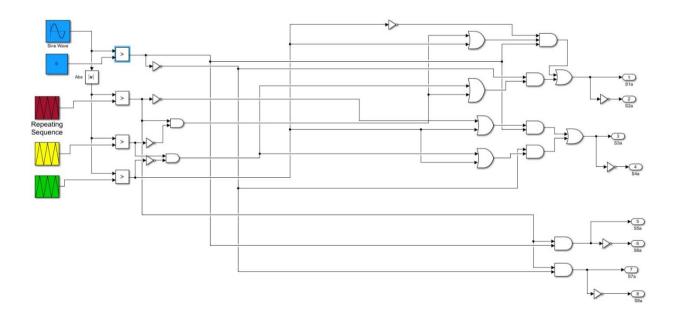

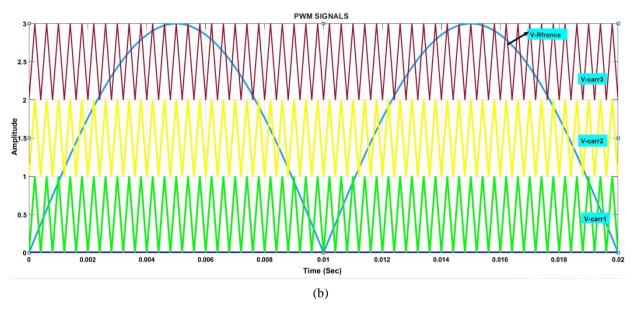

Fig .3. Logic for PWM Signal Generation (a) Logic circuit ,(b) PWM

In multilevel inverters, the pulse width modulation (PWM) technique is used to control the switches ON and OFF states. To achieve this, improve the quality of the output voltage waveform and balance of capacitors voltage by reducing voltages ripples in it. the signal produced is in Fig.3 b by simple level shifted pulse modulation (PWM).three high-frequency triangular waveforms (Vcarr1, Vcarr2, and Vcarr3) are compared with a rectified sinusoidal reference (Vref).In the PWM technique, carrier signals (Vcarr1, Vcarr2, and Vcarr3) are shifted and in a similar phase. It is also working for higher and lower switching frequencies. the result of the comparator between reference signals and carrier signals is subjected to a suitable logic circuit[3]. which generates the level information for the output voltage to be produced as shown in Fig. 3. (a). For such an arrangement, the modulation index is given as:

$$Ma = \frac{Vref}{3\,Vcarr} \tag{1}$$

#### 2.4 Capacitor analysis

The states of operation listed in Table I was successfully arranged in one cycle of output voltage, taking into account

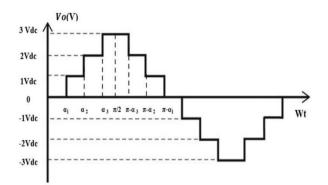

the staircase output voltage depicted in Figure 4, to balance the two capacitors. wherein  $\alpha_1$ ,  $\alpha_2$ , and  $\alpha_3$  are conducting angles. C<sub>1</sub> is used for double the voltage of **2Vdc** in the range of  $\alpha_2$  to  $\alpha_3$  during the positive half cycle. C2 is used for the voltage of 2Vdc from  $\pi$ -  $\alpha_3$  to  $\pi$ -  $\alpha_2$ . And from  $\alpha_3$ to  $\pi$ -  $\alpha_3$  both C1 and C2 provide **3Vdc**. For the negative half cycle, a similar arrangement is also made. As a result, [14] is used to express voltage ripples across the two capacitors:

$$\Delta \mathbf{Vc1} = \frac{1}{2\pi f C1} \int_{\alpha 2}^{\pi - \alpha 3} io1 \, d(wt)$$

$$\Delta \mathbf{Vc1} = \frac{1}{2\pi f \, c1} \int_{\alpha 2}^{\pi - \alpha 3} ic1 \, d(wt) \tag{2}$$

(3)

where *V-ref* is the reference signal amplitude, and *V-carr* is the triangular carrier signal amplitude. Only the switching state  $\Delta Vc2 = \frac{1}{2\pi f C2} \int_{\alpha 3}^{\pi - \alpha 2} io2 \ d(wt)$  combination of switching states 2 and 8 with 3 and 7 will result in an equal power-sharing between the capacitors  $C_1$  and  $C_2$  because  $c_2 = \frac{1}{2\pi f C1} \int_{\alpha 3}^{\pi - \alpha 2} ic2 \ d(wt)$  of the symmetrical charging and discharging. Thus, there will be no difference in the voltage ripple between them. The level

indicator signals and Table I are used to create the gating signals.

For example, if the selected combination of states is 2 and 8 with here io is the output current of the inverter and f is the and 6, Switch S2 must be turned ON for states 2 and 4 during the equency of the output voltage.

positive half cycle and 8 and 9 during the negative half cycle. The output current (io=Vo/R), io is inversely proportional level outputs for these states are tapped, and the gating pulse signathe Vo, when the load is used as a purely resistive R. is generated after the proper logic has been used. Similar progresse ripples of voltage can be described as:

is repeated to derive gating pulse signals for the switches'

remaining modes.

Fig .4. Operation describes how the 7-level inverter is configured for stair output.

$$AVC1 = \frac{(3\pi - 4\alpha 3 - 2\alpha 2)Vdc}{(4)}$$

$$\Delta VC2 = \frac{(3\pi - 4\alpha 3 - 2\alpha 2)Vdc}{2\pi fC2}$$

(5)

It indicates that there is no difference in the voltage ripple between the two capacitors. Both capacitors operate twice, once in the positive half cycle and the negative half cycle alternately. the capacitor voltage ripple can be controlled by a suitable switching method.

#### **3-Selective Harmonic Elimination technique**

To eliminate the odd harmonics and control the fundamental voltage, the selective harmonic eliminated pulse width modulations (SHE-PWM) method is used to find the optimum switching angles, specifically  $(\alpha_1, \alpha_2, \dots, \alpha_n)$ . The Fourier series can be used to express the output voltage (Vo) waveform mathematically[17]:

$$\mathbf{Vo} = \mathbf{ao} + \sum_{i=0}^{n} \mathbf{an} \cos\left[\frac{2\pi nf}{T}\right] + \mathbf{bnsin}\left[\frac{2\pi nf}{T}\right]$$

(6)

For the symmetric staircase waveform with a quarterwave, see Fig.4.The amplitude of the dc component equals zero  $(a_0=0)$ , and The amplitude of all even harmonics equals zero (**bn=0**). the fundamental component's, **n=1**, and odd harmonic component's amplitudes are given by:

$$V_{I} = \left[ \left( \frac{4Vdc}{\pi} \right) \sum_{K=1} \cos(\alpha k) \right]$$

$$[(4Vdc) = 0$$

(7)

$$Vn = \left[ \left( \frac{4Vdc}{n\pi} \right) \sum_{K=1} \cos(n\alpha k) \right]$$

(8)

Where  $\alpha k$  is the switching angles, n is odd harmonics, and the staircase waveform's switching angles will be adjustable to obtain the output voltage THD with the lowest possible. The total harmonic distortion (THD) is represented as follows:

$$\mathbf{THD} = \sqrt{\frac{\sum V n^2}{V 1^2}} \tag{9}$$

Five categories of finding three firings are included in the suggested topology to find the lower-order harmonics in the waveform angles of the output voltage waveform. The topology of a seven-level inverter,( 3rd,5th,7th,9th,11th) odd harmonic is selected from the output voltage waveform for harmonic elimination. the firing angle ( $\alpha_1$ ,  $\alpha_2$ ,  $\alpha_3$ ) that was calculated using the constraint relationship  $[0 < \alpha_1 < \alpha_2 < \alpha_3 < \pi/2]$  is calculated using equation (10):

$\frac{4V}{1-1}[\cos(\alpha 1) - \cos(\alpha 2) - \cos(\alpha 3)]$

$$V_n =$$

(10)

In the output voltage waveform, the 3rd harmonic (n=3), 7th harmonic (n=7), etc were eliminated[18].

$$V_{9=\frac{4V}{9\pi}}[\cos(9\alpha 1) - \cos(9\alpha 2) + \cos(9\alpha 3)]$$

# $V_{11=\frac{4V}{11\pi}}[\cos(11\alpha 1) - \cos(11\alpha 2) + \cos(11\alpha 3)]$

To reduce the (3rd,5th,7th,9th, and 11th )harmonics in the output waveform, It has been set so that the corresponding voltage is zero. Utilizing the selective harmonic elimination technique, with the smallest number of switching and selecting the optimum firing angles, only particular harmonics are eliminated. This method is ideal for controlling inverters. This method makes it possible to obtain a low THD output waveform without the use of a filter circuit. Another method reduces THD by optimizing the switching angle using a genetic algorithm.

#### 3.1 Genetic Algorithm(GA)

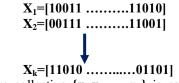

The goal is to determine the optimal switching angles that result in an output voltage with the required fundamental component and the fewest of THD that is logically possible. . An optimization algorithm should be used to resolve this issue. a genetic algorithm is used in this work. which is a simple, powerful, and evolutionary method inspired by the concepts of genetics and natural selection. It is a general-purpose stochastic global search algorithm that looks for solutions without considering functional derivative data. which reduces (or expands) a given objective function. While addressing complex objective functions, GA reduces computation and search time requirements [19]. The SHE-PWM technique's genetic algorithm is still an innovation. . To minimize the function  $f(\mathbf{x}_1, \mathbf{x}_2, \dots, \mathbf{x}_k)$  using **GA**. The first step is to encode each Xi as a length binary or floating-point string. A binary string, such as in the following:

Where collective  $\{x_1, x_2, \dots, x_k\}$  is called a chromosome, and xi is the genes.

#### 3.2 Defining The Issue

Any application uses the same GA methodology. A GA only requires a small number of parameters to be set for it to function. The following are the procedures for formulating a problem and using the GA:

1- Choose between floating-point or binary strings.

2- Identify the variables that are important to the subject; this amount will stand in for the number of genes on a chromosome. The number of variables and the number of programmable switching angles is the same in this application. For a seven-level inverter, each chromosome

will have three switching angles, or. ( $\alpha 1$ ,  $\alpha 2$ ,  $\alpha 3$ ). 3- Define the population size and start it out. The higher population may speed up convergence but at the expense of longer execution times. When initializing the population with random angles between 0 and 90, consideration is given to the output voltage waveform's quarter-wave symmetry.

4- The cost function is the most crucial component in the GA evaluation of each chromosome's fitness. This study aims to reduce the output voltage's total harmonic distortion. In light of this, the cost function Fv is written as.

Fv

$$(\alpha_1, \alpha_2, \alpha_{3)=} \sqrt{\frac{\sum_{n=3,5,7...}(Vn)^2}{V1^2}}$$

(12)

number of iterations in order to find a solution (20 in this connected in series. Therefore, to ensure capacitor voltage case). FVs are used to identify new offspring after the initial equalization, iteration. These undergo crossover and mutation processes, balancing circuits are needed. In contrast, capacitors' and a new population is produced that follows the same cycle voltage in [13], [14], can be connected in parallel multiple beginning with FV assessment. Sometimes, well before the times during one cycle of output voltage with the input 20 iterations are finished, the GA can converge to a solution. voltage source Vin, and the suggested one can be The answer must also meet the following fundamental automatically balanced as a result. Additionally, as two Hconstraint[20]:

#### $[0 < \alpha_1 < \alpha_2 < \alpha_3 < \pi/2]$ (13)

### 4-Comparison with Other Recent SCMLI Topologies:

Parameters comparison with existing seven-level inverters is capacitors voltages overall. made in Table II. wherein E represents one level of the output

$voltage, (Nswitches(N_{SW}), Nsource(N_{SO}), Ndiode(N_D), Ncapaci \ 5-Results \ and \ Discussion$

$tance(N_C)$ , and N-level $(N_L)$ ) represented the number of power semiconductor switches, DC source, and diodes, capacitors, A less complicated and effective model has been and, output level inverter respectively.

Т TSV C-Gain N<sub>SW</sub> Nso  $N_{C}$  $N_{D}$ N<sub>L</sub> Balance [12] 7 3 3 2 7 15E NO 1 7 16 3 0 YES [13] 1 16E 3 [14] 2 0 7 16E YES 3 16 1 3 7 1.5 [15] 10 2 0 16E YES 3 3 7 [16] 6 8 14E NO 1 8 2 2 7 3 P.w 1 16E YES

Table 2

Parameters Comparision of 7-Level inverters

proposed 7-level inverter topology(**p.w**) The is а symmetrical circuit comprised of a single DC source of Vdc=100V. For inverter configuration, the prime parameter is Total Standing Voltage (TSV). It is the summation of the absolute voltage across every switching device, while the same voltage stress occurs in the

Seven-Level Inverter Topology

complementary switch. Complementary switches,  $(S_1, S_1)$ )and (S<sub>2</sub>, S<sub>2</sub>'):

$$Vs_1 = Vs_1' = Vs_1 = Vs_1' = V_{dc}$$

(14)

Complementary switches, S<sub>2</sub>, S<sub>3</sub>' and S<sub>4</sub>, S<sub>4</sub>'

$$Vs_3 = Vs_3' = Vs_4 = Vs_4' = 3V_{dc}$$

(15)

$$TSV = \sum_{y=1}^{8} V sy \tag{16}$$

Therefore, substitute (14)–(15) in (16) yields: TSV=16 Vdc

The TSV of MLIs is 16Vdc and the TSV p.u. is computed by[21],

$$TSV p.u = \frac{TSV}{Vo, peak} = \frac{16 V dc}{3 V dc} = 5.333 p.u$$

(17)

Where **Vo,peak** is the maximum output voltage.

The Voltage gain

$$=\frac{Vo.peak}{Vdc} = \frac{3}{1} = 3$$

(18)

The work [16] uses the fewest switches overall but the most diodes compared to the works [13] and [14], which both use the most switches but no diodes. However, the total switch voltage (TSV) is essentially constant across all inverters. The works [12], [13], [15], and [16] all use three capacitors, whereas [14] and the proposed one only need two.

The three capacitors in [12] and [16] to divide the input 5-The GA is typically set up to run for a predetermined voltage and maintain the balance of the voltage, are often modulation techniques or additional bridges are formed by the eight power switches used in this proposed work, The proposed inverter benefits from a simpler design, step-up capability, and self-balancing

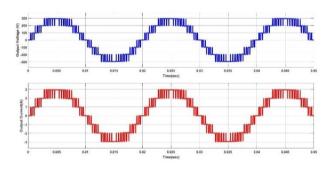

constructed. It is investigated and assessed to show the significance and contribution of the suggestion inverter of seven levels in the Matlab simulation program. The requirements and elements are listed in TableIII and the source voltage is 100Vdc. The PWM level shift is used to gating pulses control of the power semiconductor switches, wherein V-reference is equal 50Hz and V-carrier is equal to 2.5 kHz, and the Ma is set to 1. A 2200 µF capacitance was chosen for  $C_1$  and  $C_2$  respectively to minimize the capacitor ripple voltage. The resistive load of 100 ohms in the inverter and according to waveforms of output voltage, current.

#### Table 3 Simulation parameters of the proposed 7-1 inverter

#### Hussein S. Abdulazeez et al

| Description           | Simulation |  |  |

|-----------------------|------------|--|--|

| Source Voltage (Vin)  | 100 V      |  |  |

| Load Voltage (Vo)     | 300 V      |  |  |

| Carrier's frequency   | 2.5KHz     |  |  |

| Fundamental frequency | 50Hz       |  |  |

| Switching frequency   | 2.5KHz     |  |  |

| Capacitor (C1)        | 2200 µF    |  |  |

| Capacitor (C2)        | 2200 µF    |  |  |

| Load                  | 100 ohms   |  |  |

(c)

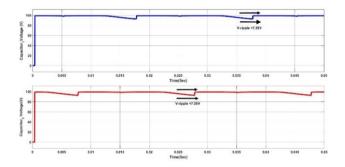

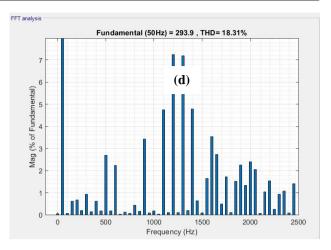

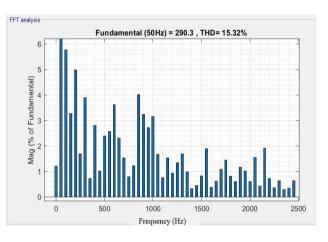

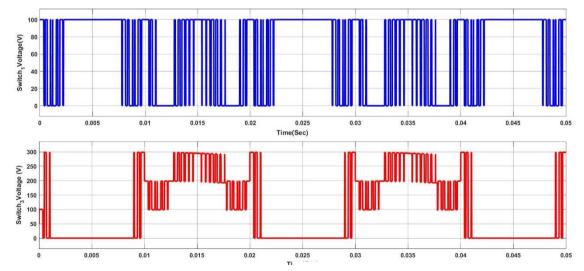

Fig. 5. Shows (a) Output voltage and load current with R load (b) capacitors Voltages (c),(d)Shows THD with GAs optimized firing angle for Ma =1 (e) Standing voltage across the switching power devices

the capacitor's voltage as shown in Fig.5 (a and b). Through this, it can see the triple reinforcement of the input source, as well as the stability in the voltages of the capacitors, which is one of the most important advantages of the work of this inverter.

The three firing angles  $(a_1,a_2,a_3)$  help to significantly reduce the THD as shown in Fig. 5(c,d) where we notice that the value of the total harmonic distortion has improved from(18,31% to 15.32%) as a result of the optimization technique used to implement the GAs optimized selective harmonic elimination.

The voltage stress of each switch in the tippler section ( $S_1$ ,  $S_1$ ',  $S_2$ , and  $S_2$ ') was 100V. and their remaining polarity section ( $S_3$ ,  $S_3$ ',  $S_4$ , and S4') is 300 volts, Fig .5.(e) shows the stress voltage across switches  $S_1$  and  $S_3$ .

These results confirm the mathematical analysis in the fourth section when comparing the proposed inverter with other studies, through which it was proved that the total standing voltage is equal to (16Vd.c).

#### Conclusions

This paper introduces a new inverter with seven levels with reduce all components of the inverter circuit. Eight switches, two diodes, two capacitors, and a single DC source make up the topology that was designed. Simple design work is produced by the output voltage's symmetrical upper and lower halves. the voltage gain Triple the input. Three firing angles were obtained using the SHE with GAs to reduce the lower order harmonics, which lower the THD value. Due to the proposed topology's ability to self-balance, the voltages of the capacitors are naturally balanced. The capacitor's voltages are maintained using a straightforward series-parallel method without any additional circuit or any sensors. The principle of operation and the simple pulse modulation method were discussed. The results of comprehensive and detailed studies are presented, and the operability and viability of the suggested topology are validated. Finally, A detailed comparison with the other operating topologies in terms of decreased components confirms the merits of the suggested topology.

It can be used as another optimization technique to improve THD and replace the D.C source with photovoltaic (PV) modeling in future works.

#### References

[1] Franquelo LG, Rodriguez J, Leon JI, Kouro S, Portillo R, Prats MA. "The age of multilevel converters arrives". IEEE industrial electronics magazine. 2008 Jun 17;228.

[2] Gupta KK, Ranjan A, Bhatnagar P, Sahu LK, Jain S. "Multilevel inverter topologies with reduced device count: A review". *IEEE Transactions on Power Electronics*. 2015 Feb 26;31,135.

[3] Sandeep N. "A 13-level switched-capacitor-based boosting inverter". *IEEE Transactions on Circuits and Systems II: Express Briefs.* 2020 Aug 18;68,998.

[4] Máthé L, Séra D, Kerekes T. "Three-phase photovoltaic systems: Structures, topologies, and control". *Renewable Energy Devices and Systems with Simulations in Matlab® and Ansys; CRC Press: Boca Raton, FL, USA*. 2017,67.

[5 Hosseini SH, Gharehkoushan AZ, Tarzamni H. "A multilevel boost converter based on a switchedcapacitor structure". *In2017 10th International Conference on Electrical and Electronics Engineering (ELECO)* 2017 Nov 30 (. 249). IEEE.

[6] Forouzesh M, Siwakoti YP, Gorji SA, Blaabjerg F, Lehman B. "Step-up DC-DC converters: a comprehensive review of voltage-boosting techniques, topologies, and applications". *IEEE transactions on power electronics*. 2017 Mar 6;32,9143.

[7] Sathik MJ, Sandeep N, Almakhles D, Blaabjerg F. "Cross connected compact switched-capacitor multilevel inverter (C 3-SCMLI) topology with reduced switch count". *IEEE Transactions on Circuits and Systems II: Express Briefs.* 2020 Apr 15;67,3287.

[8] Sathik MJ, Bhatnagar K, Sandeep N, Blaabjerg F. "An improved seven-level PUC inverter topology with voltage boosting". *IEEE Transactions on Circuits and Systems II: Express Briefs*. 2019 Mar 5;67,127.

[9] Samadaei E, Gholamian SA, Sheikholeslami A, Adabi J. "An envelope type (E-Type) module: asymmetric multilevel inverters with reduced components". *IEEE Transactions on Industrial Electronics.* 2016 Jan 22;63,7148.

[10] Samadaei E, Kaviani M, Bertilsson K. "A 13levels module (K-type) with two DC sources for multilevel inverters". *IEEE Transactions on industrial electronics*. 2018 Sep 10;66,5186..

[11] Zeng J, Lin W, Cen D, Liu J. "Novel K-type multilevel inverter with reduced components and self-balance". *IEEE Journal of Emerging and Selected Topics in Power Electronics*. 2019 Sep 5;8,4343.

[12] Choi JS, Kang FS. "Seven-level PWM inverter employing series-connected *capacitors paralleled to a single DC voltage source*". *IEEE Transactions on Industrial Electronics*. 2014 Nov 14;62,3448.

[13] Choi JS, Kang FS. "Seven-level PWM inverter employing series-connected capacitors paralleled to a single DC voltage source". *IEEE Transactions on Industrial Electronics.* 2014 Nov 14;62,3448.

[14] Choi JS, Kang FS. "Seven-level PWM inverter employing series-connected capacitors paralleled to a single DC voltage source". *IEEE Transactions on Industrial Electronics.* 2014 Nov 14;62,3448.

[15] Liu J, Zhu X, Zeng J. "A seven-level inverter with self-balancing and low-voltage stress". *IEEE Journal of Emerging and Selected Topics in Power Electronics*. 2018 Nov 9;8,685.

[16] Rahim NA, Chaniago K, Selvaraj J. "Singlephase seven-level grid-connected inverter for photovoltaic system". *IEEE transactions on industrial electronics*. 2010 Aug 30;58,2435.

[17] Gera G, Bairwa RK, Kumar D. "Genetic Algorithm based Approach for Reduction of Total

Harmonic Distortion in Photo Voltaic Inverter". *International Journal of Computer Applications*. 2014;87.

[18] Siddique MD, Mekhilef S, Padmanaban S, Memon MA, Kumar C. "Single-phase step-up switched-capacitor-based multilevel inverter topology with SHEPWM". *IEEE Transactions on Industry Applications*. 2020 Jun 12;57,3107.

[19] Ozpineci B, Tolbert LM, Chiasson JN. "Harmonic optimization of multilevel converters using genetic algorithms". *In2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No. 04CH37551)* 2004 Jun 20 (5, 3911). IEEE.

[20] Dahidah MS, Konstantinou G, Agelidis VG. "A review of multilevel selective harmonic elimination PWM: formulations, solving algorithms, implementation and applications". *IEEE Transactions on Power Electronics*. 2014 Sep 5;30,4091.

[21] Kannan M, Kaliyaperumal S. "A High Step-up Sextuple Voltage Boosting 13S-13L Inverter With Fewer Switch Count". *IEEE Access. 2021 Dec 8;9:164090.*