Available at http://jeng.utq.edu.iq engjrnal@jeng.utq.edu.iq

### **Simulation Action Potential Signal Based On FPGA**

#### Nabil Jalil Aklo

Biomedical Engineering Department, University of Thi-Qar, Thi-Qar, Iraq.

#### Abstract

This paper aim to generate and take Action potential signal (AP) then converts it to digital signal based on one bit Sigma-Delta converter ( $\sum$ - $\Delta$ ) to produce a 1-bit stream represent this signal with resolution of 10 bit. This data has been stored in proposed memory created in electronic device called Field Programmable Gate Array (FPGA) by which also the proposed converter had been designed and implemented practically. Finally, the obtained results analyzed and compared with other converter techniques to show the difference in the results and performance. *Keywords:* Action potential; Sigma-Delta Converter; FBGA.

#### 1. Introduction

The rapid and great development of the electronics industry has led to the ease of design and manufacture of electronic circuits, which in turn carry out electronic operations more accurate, high flexible and a few errors especially programmable electronic circuits such as Arduino, PLC, FPGA and etc[1]. This allows us to design and build any electronic circuit easily and without any complexity, which reduces the cost of manufacturing and the power consumption, in addition reducing the error rate in the circuit and also allows us to change the design at any time without the need to install new elements into this circuit[2]. Aim of this work is to generate and convert analog signal to digital signal and process it. The signal that had been processed in this paper is biological signal called Action Potential signal(APS). This signal had been converted by using Sigma-Delta analog to digital converter ( $\Delta$ - $\sum$  ADC) which designed based on Field Programmable Gate Array (FPGA) to decrease hardware and cost.

#### **1.1 Action Potential Signal(APS)**

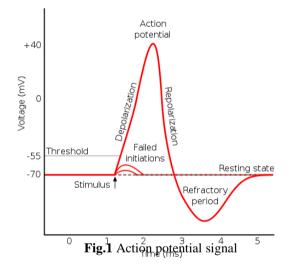

The brain control on the organs using nerves connected to it as a complex network, where the brain send orders to the members depending on electric signals produced chemically, this signals called action potential signals (APS). To simulate this signal and deal with, we must know its behavior. Figure 1 illustrate the Approximate shape of action potential signal, when the neuron is stimulated to the threshold level the signal will be upraised to peak value at 40mv with time 2ms and then falls to -90 at time 3ms[3]. We note from the curve the signal carry on exponentially.

### **1.2** First Order Sigma-Delta Analog to Digital Converter( $\sum \Delta$ )

First Order Sigma-Delta Analog to Digital Converter( $\sum \Delta ADC$ ) convert analog signal to one bit stream digital signal, this property make the system simple and reduce

the complexity as well as hardware[4]. The most important feature in this converter is it use very high sampling rate.

The use very high sampling ratio has several benefits summarized below[5]:

- No strict requirements obligatory on analog building blocks.

Low cost, low power consumption in digital filtering.

Reduced baseband quantization noise power.

- High resolution of the digital output and better noise shaping.

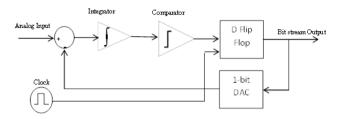

The Sigma-Delta converter consist of a summer, an integrator, a comparator, a D flip-flop and a DAC as shown in the figure 2, the output of the converter is 1-bit stream converted by 1-bit digital to analog converter then fed back to compare it again with input signal[6].

#### **1.2.1 Sigma-Delta Converter Verification**

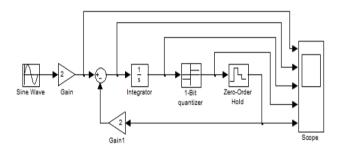

To verify the converter we had been designed it using Matlab/Simulink. Figure 3 illustrate the block diagram of

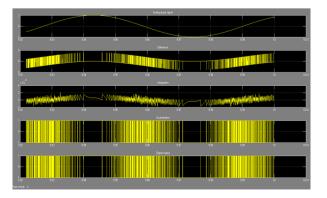

the system, figure 4 contain multi outputs represent the stages of signal passing through the converter,

Fig. 2 Sigma-Delta Analog to Digital converter

The signal that used in verification is sinusoidal, we note from the figure the input wave compared with feedback signal which regard analog signal converted from digital output then integrated and quantized to several level to obtain proper resolution, this signal translated to a group of ones and zeros.

Fig. 3 Sigma-Delta Analog to Digital converter representation in Matlab/simulink

#### 2. Hardware Implementation

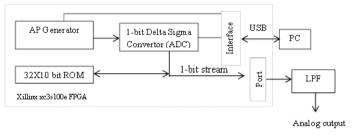

The system consist of (APS) generated according eq. 1 in the programmable electronic device called FBGA then converted to digital signal by input it to 1-bit Sigma-Delta converter instead of use multi bit converters to reduce the hardware and quantization noise also power consumption in this case we use 10 bit resolution after this stage the signal converted to analog using Low Pass Filter (LPF) with attenuator resistance. Figure 5 illustrate the block diagram of the whole system.

Fig. 4 Output of verification system

Fig.5 Block Diagram of the system

#### 2.1 FPGA Unit

Digital FPGA structure offer a important speedup and real time signals over software designs, also size, weight, and power consumption efficiency. Compared to analog devices, digital FPGAs designs are stable and flexible in design alterations[7].

#### 2.2 Low Pass Filter

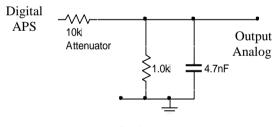

The final stage of the system is the LPF that converts the digital signal to an analogue signal, figure 6 shows the attenuator and the RC filter to decrease the magnitude of high frequency[8].

Fig.6 LPF Attenuator

#### **3. Experimental results**

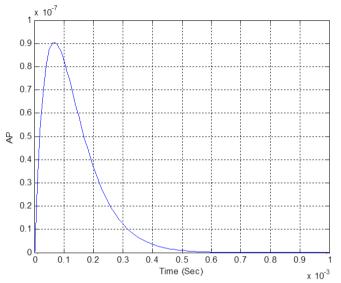

APS signal is produced practically by built in designed generator in the FPGA as shown in the figure 7 according to the equation[8]:

Where A and B are constants and n is an integer and its typical value is:

A=3.7\*10-3Vs-1, B= 1.5\*104s-1 and n=1.

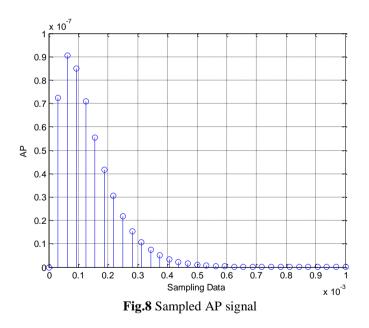

The magnitude of A,B and n can be changed to obtain waveform with specific options. This property increase the flexibility of the system where we can make the signal easier and faster without need to change or modify the software code or the hardware design. APS signal sampled where its duration is 0.64ms with 32 sample according sample frequency 48.828k sample/s as shown in the figure 8, each sample is represented by 10-bit binary number covering integer and decimal parts in it(show table 1) to make the conversion more precise and decrease the loss in the signal as well as decrease the ripple. Data conversion to binary require convert the integer and decimal part of the sample value, in this work we take three digit after point and make conversion by fixed point method using MATLAB code.

Fig.7 Output of the verification system

In table 1 some samples had been taken to show the procedure by which the conversion done where the actual signal value processed to obtain fixed point value, this is rounded to the nearest integer value after this stage the signal is converted to digital (Hexa) to dealwith it.

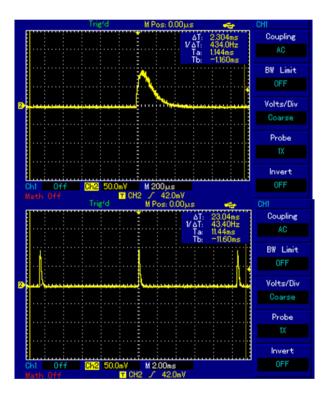

Figure 9 shows the APS signal obtained practically using FPGA with  $200\mu s/div$  horizontally and 500mv/div vertically.

The on-board 50 MHz clock is used as the timing reference for the Sigma-Delta converter generator. For the required 10 bit data precision, the Sigma-Delta converter sample rate is kept at just under 50kHz (48.8kHz to be exact) which is adequate for the generation of APS.

Table 1 illustrate some samples values of the signal

| No. | Actual<br>Value (mv) | Fixed point<br>Value | Rounded<br>value | Hexa<br>Value |

|-----|----------------------|----------------------|------------------|---------------|

| 1   | 0.1785601            | 178.5601             | 179              | B3            |

| 2   | 0.2989427            | 298.9427             | 299              | 12B           |

| 3   | 0.0712363            | 71.2363              | 71               | 047           |

| 4   | 0.0366962            | 36.6962              | 73               | 025           |

| 5   | 0.0042040            | 4.2040               | 4                | 004           |

| 6   | 0.001970             | 1.9707               | 2                | 002           |

Fig.9 AP signal obtained practically

The overall system takes up only 35% of the available FPGA slices and total CPU time to Xst completion: 0.36 secs, as illustrated in the table 2 thereby suggesting that further savings could be achieved if the design was implemented on a custom circuit board.

# **3.1** Case study 1: Analog to digital converter design by Pulse Width Modulation (PWM) instead of sigma-delta method.

A.Al-Shueli, and C.T. Clark[9] had been designed Analog to digital converter using FPGA but by using Pulse Width Modulation (PWM) technique, where we see the total used memory 38% compared with our work that use 35% also the power consumption using Sigma-Delta is 15.98mW while by using PWM became22.56mW. Table 3 shows the comparison between utilization of Common components in FPGA using Sigma-Delta and PWM technique, where we note that the number of used component by PWM method is more than Sigma-Delta method this lead to use high size memory as well as there is saving in the power due to using the second method.

**Table 2** illustrates

FPGA utilization summary

| Device Utilization Summary                    |      |           |             |         |  |

|-----------------------------------------------|------|-----------|-------------|---------|--|

| Logic Ublization                              | Used | Available | Utilization | Note(s) |  |

| Number of Sice Flip Flops                     | 36   | 1,920     | 1%          |         |  |

| Number of 4 input LUTs                        | 658  | 1,920     | 34%         |         |  |

| Number of occupied Slices                     | 343  | 960       | 35%         |         |  |

| Number of Sices containing only related logic | 343  | 343       | 100%        |         |  |

| Number of Sices containing unrelated logic    | 0    | 343       | 0%          |         |  |

| Total Number of 4 input LUTs                  | 676  | 1,920     | 35%         |         |  |

| Number used as logic                          | 33   |           |             |         |  |

| Number used as a route-thru                   | 18   |           |             |         |  |

| Number used as Shift registers                | 625  |           |             |         |  |

| Number of bonded 108s                         | 7    | 83        | 8%          |         |  |

| 108 Flip Flops                                | 1    |           |             |         |  |

| Number of BUFGMUXs                            | 1    | 24        | 4%          |         |  |

| Average Panout of Non-Clock Nets              | 1.31 |           |             |         |  |

## **Table 3** shows the comparison between utilization ofCommon components FPGA using Delta-Sigma andPWM technique

| N<br>o. | Item                          | Used            |                 | Avail | Utilization<br>(%) |         |

|---------|-------------------------------|-----------------|-----------------|-------|--------------------|---------|

|         | Rem                           | Δ-Σ             | PW<br>M         | able  | Δ-<br>Σ            | PW<br>M |

| 1       | Number of slice flip<br>flop  | 36              | 45              | 1920  | 1%                 | 2%      |

| 2       | Number of 4 inputs<br>LUTS    | 658             | 726             | 1920  | 34<br>%            | 37      |

| 3       | Number of occupied slices     | 343             | 380             | 960   | 35<br>%            | 39      |

| 4       | Number used as logic          | 33              | 101             |       |                    |         |

| 5       | Number used as shift register | 625             | 625             |       |                    |         |

| 6       | Number of bonded<br>IOBs      | 7               | 8               | 83    | 8%                 | 9%      |

| 7       | Memory used                   | 35%             | 38%             |       |                    |         |

| 8       | Power consumption             | 15.9<br>8m<br>W | 22.5<br>6m<br>W |       |                    |         |

## **3.2** Case study 2: Design Sigma-Delta ADC by Microcontroller instead of FPGA.

Anju Ashok, Anusha Zachariah[10] had been designed Sigma-Delta ADC by microcontroller. In this method we note the design of converter pass through four stage (Coding, Compiling, Simulation, and Burning), these stage require external hardware implementation and additional programs while FPGA outline all this stage in it without need to external devices (complexity less) as well as FBGA run the conversion faster compared with microcontroller. Also the power consumption in FBGA regard few compared with microcontroller.

Fig.10 Delta Sigma converter implementation

| Mem[0]        | Mem[8]=1 | Mem[16]= | Mem[24]= |

|---------------|----------|----------|----------|

| =12'h000:     | 2'h0C0   | 12'h026  | 12'h006  |

| Mem[1]        | Mem[9]=1 | Mem[17]= | Mem[25]= |

| =12'h0B7      | 2'h0A1   | 12'h01E  | 12'h004  |

| Mem[2]        | Mem[10]= | Mem[18]= | Mem[26]= |

| =12'h112      | 12'h086  | 12'h018  | 12'h003  |

| Mem[3]        | Mem[11]= | Mem[19]= | Mem[27]= |

| =12'h133      | 12'h06E  | 12'h013  | 12'h003  |

| Mem[4]        | Mem[12]= | Mem[20]= | Mem[28]= |

| =12'h132      | 12'h05A  | 12'h00F  | 12'h002  |

| Mem[5]        | Mem[13]= | Mem[21]= | Mem[29]= |

| =12'h11E      | 12'h049  | 12'h00C  | 12'h002  |

| Mem[6]        | Mem[14]= | Mem[22]= | Mem[30]= |

| =12'h101      | 12'h03B  | 12'h009  | 12'h001  |

| Mem[7]=12'h0E | Mem[15]= | Mem[23]= | Mem[31]= |

| 0             | 12'h02F  | 12'h007  | 12'h001  |

Table 4 illustrate Peak Memory Usage: 159 MB

#### 4. Conclusion

In this paper, first order Sigma-Delta analog to digital converter is designed and implemented practically on FPGA, LPF and attenuator. Action potential signal is taken and converted to 1-bit stream digital signal with 10 bit to increase the resolution. The results obtained were compared with other results got from the use of different methods, whether different devices like micro controller or techniques used like PWM, where it provide a abbreviation in the hardware implementation and power consumption as well as decrease the complexity of the circuit.

#### 5. References

[1] Sayandwip Sarkar and Arvind Choubey, "FPGA Implementation of All-Digital Adaptive Delta Sigma Modulator with Enhanced SQNR and Dynamic Range", CONECCT 2015 1570121521, 978-1-4799-9985-9/15/\$31.00 ©2015 IEEE.

[2] Mohammed Arifuddin Sohel, 2K. Chenna Kesava Reddy, "Design of Low Power Sigma Delta ADC", 3Syed Abdul Sattar, International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.4, August 2012.

[3] Tom A. D. Riley, Member, IEEE, Miles A. Copeland, Fellow, https://en.wikipedia.org/wiki/Action\_potential.

[4] IEEE, and Tad A. Kwasniewski, Member, IEEE, "Delta-Sigma Modulation in Fractional-N Frequency Synthesis", IEEE Journal Of Solid-State Circuits, Vol. 28, No. 5. May 1993.

[5] Juan Yaquian Ali Niknejad,"Analysis and Design of a High Speed Delta-Sigma Modulator for mm-Wave Imaging Applications" Technical Report No. UCB/EECS-2012-76, Electrical Engineering and Computer Sciences University of California at Berkeley, May 10, 2012.

[6] Song Hongzhi, Wu Jie and Ma Yichao, "A FPGAbased 7-order 1-bit Sigma-Delta Modulator for Highprecision Signal Generation", The Ninth International Conference on Electronic Measurement & Instruments ICEMI'2009, 978-1-4244-3864-8/09/\$25.00 ©2009 IEEE.

[7] Timothée Levi, Farad Khoyratee, Sylvain Saïghi, Yoshiho Ikeuchi, "Digital implementation of Hodgkin-Huxley neuron model for neurological diseases studies", 22th International Symposium on Artificial Life and Robotics, Jan 2017, Beppu, Japan.

[8] A.I.Alshueli, "Signal Processing for Advanced Neural Recording System", PHD Thesis, University of Bath. Bath,UK, 2012.

[9] A.Al-Shueli, and C.T. Clark and J.T. Taylor, " Simulated Nerve Signal Generation for Multi-Electrode Cuff System Testing", International Conference on Biomedical Engineering and Biotechnology, IEEE. DOI 10.1109/Icbeb.2012345,2012.

[10] Anju Ashok, Anusha Zachariah, " Detection of Coloured Objects by the Implementation of Sigma Delta ADC", International Journal of Advanced Research in Electronics and Communication Engineering (IJARECE) Volume 4, Issue 4, April 2015.